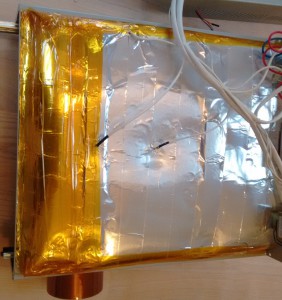

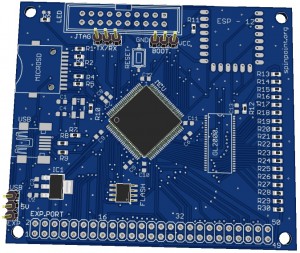

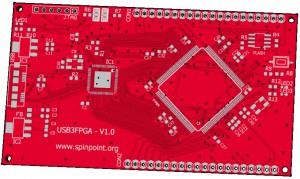

Description and purpose of the “M4 board”.

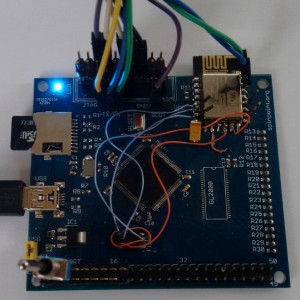

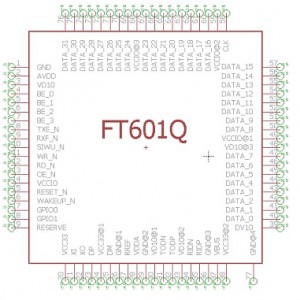

The M4 board, features as previously described a ST32F407 Cortex M4 MCU, connected via SPI to a ESP8266 WIFI module, and 18 GPIO’s routed via a GTL2000 voltage translator chip.

It was meant to be connected to the old the Amstrad CPC (z80 based) computer via it’s expansion port.

As with most old age computers, it runs with 5V I/O, here is where the GTL2000 chip came in handy.

The signals driven through the GTL2000 are output signals and the bi-directional data bus (D0-D7).

Input signals are connected directly to the ST32F407 Cortex M4 as it is 5V tolerant.

The idea was to provide WiFi to the Amstrad CPC, for easy and fast data exchange between it and a PC, but also direct internet access.

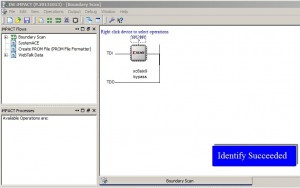

ROM BOARD emulation

First prerequisite was the ability to run code on the Amstrad via the M4 MCU so no additional loading (i.e. disc) would be needed.

It would be done by mapping a ROM in the Amstrad addressable space, this ROM would be in the M4 ram.

IORQ and WR will occur when a ROM is selected, data lines will contain the ROM number.

ROMEN and RD will occur when a read is happening from the currently selected ROM, address lines have the address, ROM data will be send back over the data lines.

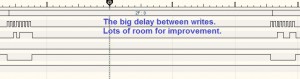

A fairly trivial task, but the timing is tight having to bit bang the gpio, do direction changes on gpio’s mapped as data lines, even when the bus runs at only 4MHz.

Much time spent optimizing the handler in ARM assembler, it finally worked.

SD card storage

Being able to run code via the ROM board emulation, it would be nice to have native r/w storage.

A micro SD card slot connected to the M4 SDIO lines, was meant for this purpose.

An transfer interface from the Amstrad CPC to the M4 was designed.

Two I/O ports were assigned when an IORQ happened, one for receiving data on the M4 and one for telling it data was send, so it could process.

This was done as it’s easy to store data (low clock count), but takes additional time to process them.

When the 2nd port is written, the MCU sends BUSRQ signal to the Z80 CPU, which will ‘freeze’ the z80 CPU at the end of the current cycle, now the M4 has the time it needs to process the incoming data, before resuming the Z80 CPU and responding.

Responses are done in the ROM space, which of course is read only on the CPC, but R/W on the M4, as it is kept in the M4 ram!

Next up, was to hook the system bios/firmware functions, that do file related I/O to tape and disc on the original system and re-directing them to the sdcard.

Thus native file access from the SD card is possible, providing the CPC with up to 32GB (or more) of storage via SD card.

WiFi & Internet

In short the connection between ESP8266 and the M4 was done via SPI as IPC.

To allow internet/WiFi access from the Amstrad CPC itself, it sends a command to the M4, which again sends an IPC call to the ESP.

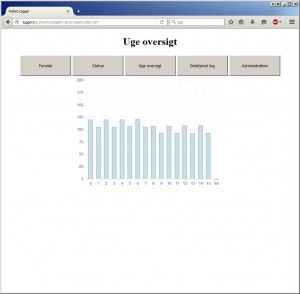

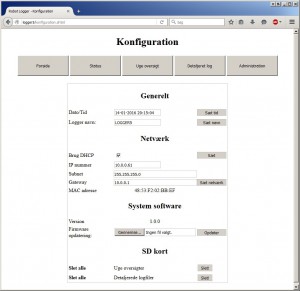

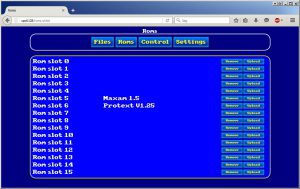

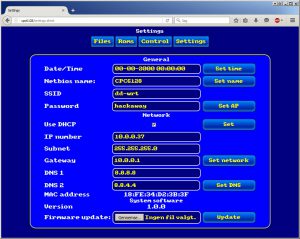

WEB interface

The ESP8266 hosts a WEB server, where various settings can be altered.

RTC

A battery mount was put on the board, making it possible to provide Real time clock as well via the RTC in the ST32F407.

What it does

Emulate Romboard, currently up to 16 roms, can be uploaded/removed via Web Interface.

Download files from internet via WiFi.

Mass storage to SD card, via native file I/O. R/W support. Emulated as drive A.

Can use DSK files on the SD card too, but only for file read access and sector reading via firmware call.

Upload files via web interface.

See a short demonstration here:

To do

Finish commands.

Lots of error checking.

Bug fixing.

More commands.

Other features.

Should anyone be mad enough to want a similar interface for their Amstrad CPC (or other suggestions), don’t hesitate to put a comment.

If enough are interested, I will run a batch + it’ll motivate me to finish and polish things up.

-Duke